JVM(八):硬件层面的并发优化

存储从底到上的顺序应该是:

远程文件的存储---磁盘---主存----L3高速缓存(这个高速缓存在主板上) (cpu共享)

---L2高速缓存---L1高速缓存---寄存器 (cpu内部)

cpu要读一个数的时候,肯定是从上往下找的,依次是:寄存器--L1--L2--L3 --主存 --硬盘--远程文件存储设备。

数据不一致的问题是如何产生的:

这样是有问题的,假如一个数在内存里,这个数会被load到L3的高速缓存里。从L3 - L2的时候,因为L2是cpu内部的,每一个cpu都有L2。

现在考虑这样一个问题,假如要读 x,y两个数,从内存里load到L3里,这都是cpu共享的,但是从L3--L2的时候,每一个cpu都有L2,那么就会load到不同的cpu的内部,假如第一个cpu把x变成1,第二个cpu把x变成2,就会产生数据不一致的问题。当第一个cpu把x改成5的时候,第二个cpu怎么才能知道第一个cpu改了呢?

怎么解决上述问题:

硬件上解决这个问题的方法是:BusLock。。cpu读L3的时候是通过系统总线的,把这个总线锁住,即:第一个cpu访问L3的时候,第二个cpu不允许访问L3,但是这种直接加锁的方法,效率偏低。。

再发展新的cpu会采用各种各样的缓存一致性协议,inter采用的是MESI协议

M Modified

E Exclusive

S Share

I invaild

cpu每个cache line标记4种状态,用额外的两位

缓存锁的缺陷是:

有些无法被缓存的数据,或者跨越多个缓存行的数据,依然要使用总线锁。

综上所述:

现代cpu的数据一致性实现就是:缓存锁(MESI)+总线锁

除了这些锁和协议以外,还有缓存行对齐的优化。

硬件层面上还优化了乱序的问题:

在硬件层面上,cpu为了提高指令的执行效率,会在一条指令的执行过程中去同时执行另一条指令,但是前提是这两条指令没有依赖关系。那么没有依赖关系的话,就可以乱序执行。

读过程无所谓,写也可以进行合并。

那么如何保证特定情况下不乱序呢?

在cpu指令级别

就是加内存屏障,注意是cpu级别的内存屏障,不是JVM的。

在intel的cpu的内存屏障,屏障两侧的指令不可重排

有sfence( s是store两个写之间加内存屏障,两个写之间不可乱序)

lfence( L是load两个读之间加内存屏障,两个读之间不可乱序)

mfence(两个读写之间加内存屏障,两个读写之间不可乱序)

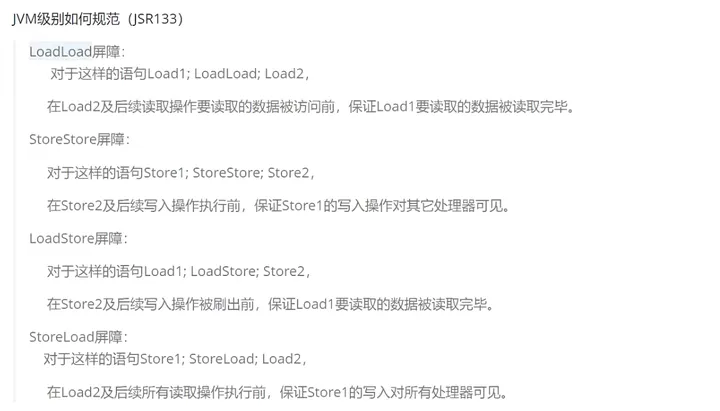

jvm级别

但是在java中,volatile有序性的保证有可能是用lock汇编指令实现的。

JVM里的有序性并不一定依赖于 硬件级别的内存屏障还可依赖于 硬件级别的lock指令

网站声明:如果转载,请联系本站管理员。否则一切后果自行承担。

- 上周热门

- 银河麒麟添加网络打印机时,出现“client-error-not-possible”错误提示 1329

- 银河麒麟打印带有图像的文档时出错 1241

- 银河麒麟添加打印机时,出现“server-error-internal-error” 1028

- 统信桌面专业版【如何查询系统安装时间】 956

- 统信操作系统各版本介绍 949

- 统信桌面专业版【全盘安装UOS系统】介绍 908

- 麒麟系统也能完整体验微信啦! 895

- 统信【启动盘制作工具】使用介绍 506

- 统信桌面专业版【一个U盘做多个系统启动盘】的方法 447

- 信刻全自动档案蓝光光盘检测一体机 392

- 本周热议

- 我的信创开放社区兼职赚钱历程 40

- 今天你签到了吗? 27

- 信创开放社区邀请他人注册的具体步骤如下 15

- 如何玩转信创开放社区—从小白进阶到专家 15

- 方德桌面操作系统 14

- 我有15积分有什么用? 13

- 用抖音玩法闯信创开放社区——用平台宣传企业产品服务 13

- 如何让你先人一步获得悬赏问题信息?(创作者必看) 12

- 2024中国信创产业发展大会暨中国信息科技创新与应用博览会 9

- 中央国家机关政府采购中心:应当将CPU、操作系统符合安全可靠测评要求纳入采购需求 8