计算机组成及原理:内部存储器

文章目录

1.存储器概述

2.静态存储器SRAM

3.动态存储器DRAM

4.高级DRAM

5.只读存储器ROM

6.FLASH闪速存储器

7.存储器总结和对比

8.并行存储器

8.1双端口存储器

8.2多体交叉存储器

9.cache存储器

ps

存储器概述

-

存储介质:目前主要采用半导体器件、磁性材料、光纪录材料等

-

存取方式:

- 存取时间和存储单元的物理位置无关,这种存储器称为随机存储器,如半导体存储器

- 存取时间和存储单元的物理位置有关,这种存储器称为顺序存储器,如磁带存储器

-

存储内容可变性:ROM,RAM

- 内容是固定不变的,即只能读出而不能写入的半导体存储器,称为只读存储器(ROM)

- 既能读出又能写入的半导体存储器,称为随机读写存储器(RAM)

-

信息易失性:断电后信息消失的存储器,称为易失性存储器

-

系统中的作用:

- 可分为内部存储器、外部存储器

- 又可分为主存储器、高速缓冲存储器等等

-

计算机对存储器理想要求:速度快、容量大、价格低、非易失

-

现状:速度快的存储器价格贵,容量小;价格低的存储器速度慢,容量大

-

多级存储器体系结构

- 高速缓冲存储器(cache):高速小容量半导体存储器,高速存取指令和数据,存取速度快,存储容量小

- 主存储器:主存,存放计算机运行期间的大量程序和数据,和cache交换数据和指令,由MOS半导体存储器组成

- 外存储器:外存,大容量辅助存储器,存储容量大,位成本低,通常用来存放系统程序和大型数据文件及数据库(磁盘存储器、磁带存储器、光盘存储器)

- cpu能直接访问的存储器称为内存储器,包括cache和主存储器

- cpu不能直接访问外存储器

-

主存储器的技术指标

- 性能指标

- 存储容量:一个存储器中可以容纳的存储单元总数

- 存取时间:存储器访问时间,一次读操作命令发出到该操作完成,将数据读出到数据总线上所经历的时间

- 存储周期:连续启动两次读操作所需间隔的最小时间,ns,存储周期略大于存取时间

- 存储器带宽:单位时间里存储器所存取的信息量。通常以位/秒或字节/秒做度量单位,是衡量数据传输速率的重要技术指标

- 性能指标

静态存储器SRAM

- 基本的静态存储元阵列

- 用一个锁存器(触发器)作为存储元,电源断电,存储数据就会丢失

- 任何一个SRAM都有三组信号线与外部打交道

- 地址线:容量

- 数据线:宽度

- 控制线:读写操作不会同时发生

- 基本的SRAM逻辑结构

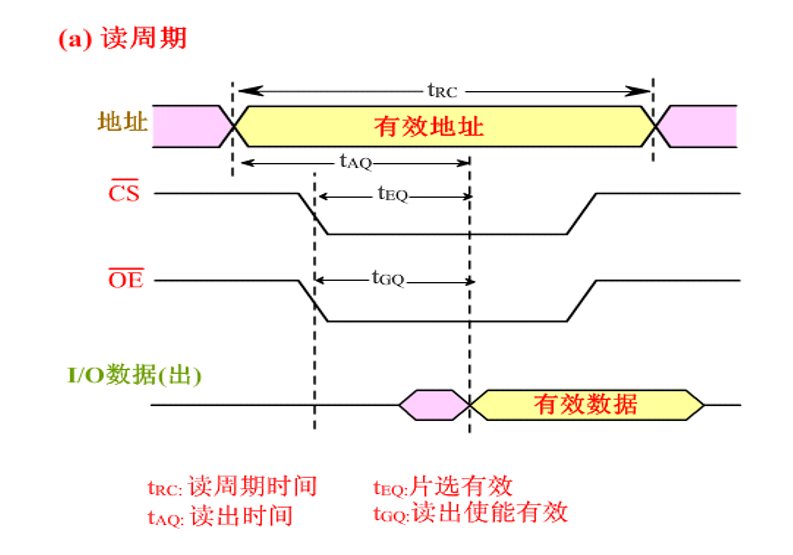

- 读写周期波形图

-

读

WE高

地址线先有效,以便进行地址译码,选中存储单元

片选信号CS和读出使能信号OE也必须有效(高电平变低电平)

从地址有效开始经Taq(读出)时间,数据总线上出校有效的读出数据

此后cs、OE信号恢复高电平,Trc以后才允许地址总线发生改变。tRC也叫读周期时间 -

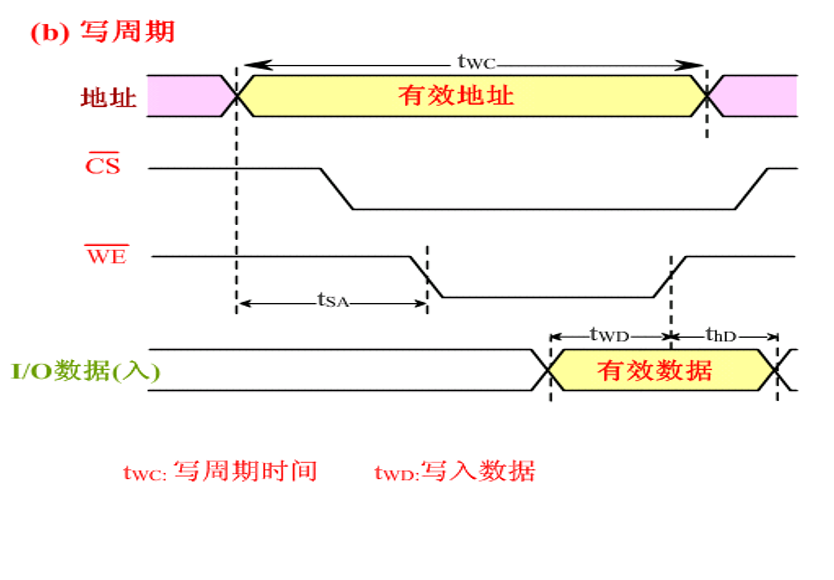

写

WE有效,低电平

地址线有效,接着片选信号CS有效,写命令WE有效(低电平),此时数据总线I/O上必须写入数据,tWD时间段内将数据写入存储器

之后撤销写命令WE和CS

I/O的写入数据要有维持时间thD,为了写入可靠

CS的维持时间也比读周期长

tWC叫做写周期时间 -

一般取tRC=tWC,即存取周期

-

动态存储器DRAM

-

速度慢,容量大,成本低

-

输入缓冲器与输出缓冲区总是互锁的

-

MOS晶体管和电容器组成的记忆电路

-

逻辑结构

- 增加了行地址锁存器和列地址锁存器。分时传送地址码:避免增加芯片地址线的管脚数目

- 增加了刷新计数器和相应的控制电路,DRAM读出后必须刷新,而未读写的存储器也要定期刷新,而且要按行刷新,所以刷新计数器的长度等于行地址锁存器

- 刷新操作与读/写操作是交替进行

-

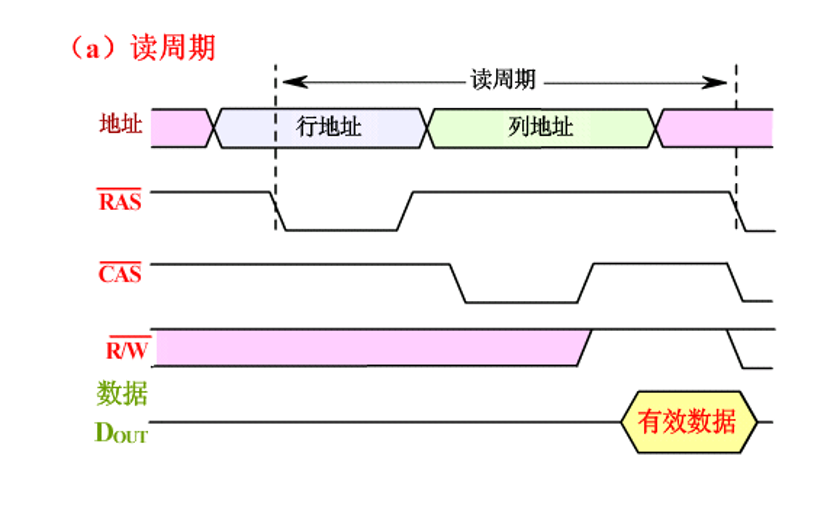

读周期

- 读出过程也是刷新过程

- 读出过程也是刷新过程

-

写周期

-

刷新周期

-

基于电容器的电荷量存储,定期刷新,保持原来记忆的正确性

-

原因:有信息电荷泄露,需定期补充

-

一般在(2ms)时间内必须刷新一次,刷新与(行地址)有关,该地址由(刷新地址计数器)给出

-

集中式刷新:DRAM所有行在每一个刷新周期中都被刷新

-

分散式刷新:每一行的刷新插入到正常的读/写周期之中

-

高级DRAM

-

FPM-DRAM:快速页模式动态存储器

-

CDRAM:带高速缓冲存储器(cache)的动态存储器

- 猝发式读取

- SRAM读出期间可同时对DRAM阵列进行刷新

- 允许写完成的同时来启动同一行的读操作

-

SDRAM:同步型动态存储器

- 这是一种与CPU实现外频Clock同步的内存模式

- 同步操作模式下,SDRAM在系统时钟的控制下从CPU获得地址、数据、控制信息 。由于采用同步控制,存储的操作与CPU的操作配合紧密,时间利用效率高,因此访问速度较快

- 通常,SDRAM支持猝发传输。由于内部结构上被分为多个存储体,其读、写、刷新可以同时进行,这也是它效率较高的原因

- 利于传送数据块

只读存储器ROM

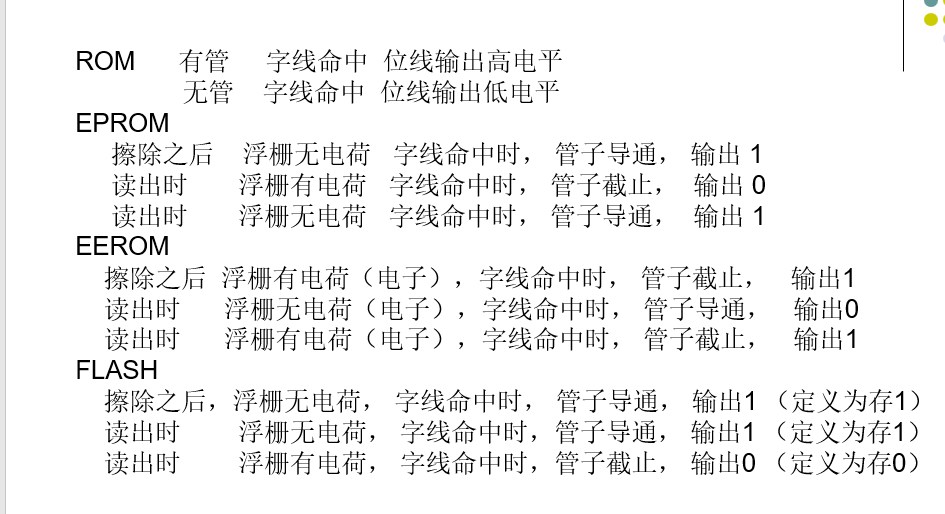

- 掩码ROM

- 可编程ROM

- PROM:一次性编程

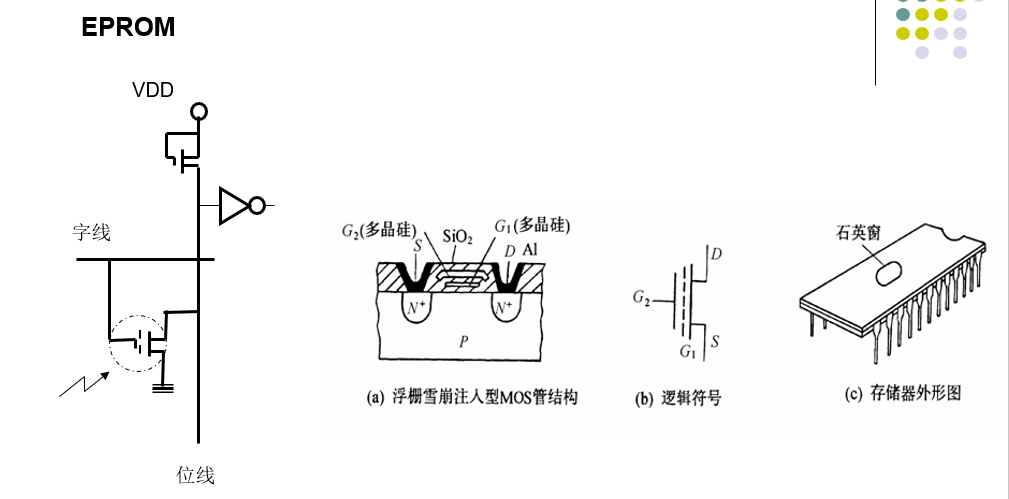

- EPROM:光擦除可编程可读存储器

浮栅雪崩注入型MOS管为存储元的EPROM

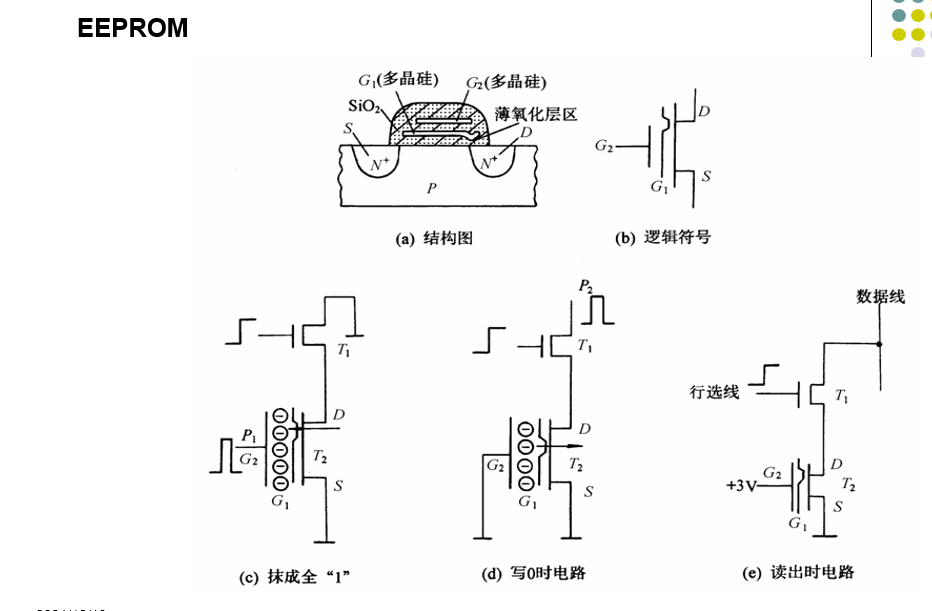

- EEPROM:电擦除可编程只读存储器

隧道效应

FLASH闪速存储器

-

高密度非易失性的读/写存储器,RAM,ROM的优点都有

-

在EPROM存储元基础上发展起来

-

NOR FLASH : RAM 内存

- 编址方式与SRAM、ROM相同,有独立的地址总线和数据总线

- 可随机访问(读或写)任意字节,可以XIP(eXecute In Place)

- 块擦除,必须先擦后写

- 读速度快,写/ 擦除速度慢

-

NAND FLASH : ROM 外存

- 按块、页编址(相当硬盘的簇、扇区)

- 只能按页(扇区)访问

- 读速度较Nor flash慢,但写、擦除较Nand flash快得多

- 占用硅片面积小,成本低

-

读速度 NOR >> NAND

-

写速度NAND >> NOR

存储器总结和对比

并行存储器

-

双端口存储器:空间并行技术

- 有两组相互独立的读写控制电路,进行并行地独立操作

- LB表示低位字节,UB表示高位字节

- 无冲突读写控制

- 有冲突的读写控制

-

多体交叉存储器:时间并行技术

- 存储器的模块化组织

- 若干模块组成的主存储器是线性编址的

- 顺序方式

- 交叉方式:实现多模块流水式并行存取,大大提高存储器带宽(单位时间二进制数信息量)

- 基本结构

- 连续读m个字所需时间T+(m-1)t

- 若干模块组成的主存储器是线性编址的

- 存储器的模块化组织

cache存储器

-

作用

- Cache 位于CPU与主存之间

- 解决CPU和主存之间的速度不匹配问题

-

基本原理

- 程序运行中具有的局部性原理(空间局部性和时间局部性特征),在CPU与主存之间引入小容量的高速SRAM

- 程序总是趋向于使用最近使用过的数据和指令,包括程序的时间局部性和程序的空间局部性

-

从功能上看是主存的缓冲存储器,由高速SRAM组成

-

除包含SRAM,还有控制逻辑,若在cpu外,控制逻辑一般与主存控制逻辑合成在一起,称为主存/cache控制器;若在cpu内,则由cpu提供控制逻辑

-

cpu与cache直接的数据交换以字为单位,cache与主存之间的数据交换以块为单位

-

性能评价

-

命中率 h=Nc/(Nc+Nm)

Nc __ 访问在cache中实现的次数

Nm__ 访问在主存中实现的次数 -

平均访问时间 ta=h*tc+(1-h)*tm :总是希望 ta 尽量接近tc

tc__ cache 访问时间

tm__ 主存访问时间

1-h _ 未命中率 -

访问效率 e = tc/ta:r = tm/tc__ 主存慢于cache的倍数

= tc/ (h*tc+(1-h)*tm)

= 1/(h+(1-h)*r)

= 1/( r+(1-r)*h)

h → 1 最好。r 为5~10为宜

-

-

主存与cache的地址映射

-

cache数据块大小称为行,主存数据块大小称为块。每块(行)由k=2^w个连续的字组成,字是cpu每次访问存储器时可存取的最小单位

-

全相连映射方式

- 将主存中一个块的地址(块号)和块的内容(字)一起存于cache的行中,分为标记部分和字部分

- 可将主存中的一个块直接拷到cache中任意一行上

-

直接映射方式

- 一种多对一的映射关系,但一个主存块只能拷贝到cache的一个特定行位置上去 i=j mod m

m为cache总行数,i为cache的行号,j为主存块号 - s位的块地址分为两部分:r位作为cache的行地址,s-r位作为标记(tag)与块数据一起保存在该行

- 一种多对一的映射关系,但一个主存块只能拷贝到cache的一个特定行位置上去 i=j mod m

-

组相连映射方式

- 存放位置灵活性和命中率前者优,电路简单和硬件投资来说后者佳,此为折中方案

- cache分为u组v行,主存块放哪组固定但哪行灵活

- m=u*v,组号q=j mod u

- 块内存地址中s位块号划分成两部分,低序的d位(u=2^d)表示cache组号,高序的s-d位作为标记与块数据一起存于此组的某行中

-

-

替换策略

- cache工作原理要求它尽量保存最新数据

- 最不经常使用算法(LFU)

- 近期最少使用算法(LRU)

- 随机替换

-

cache写操作策略

-

cache与主存内容保持一致

-

写回法

- cpu写cache命中时,只修改cache的内容,不立即写入主存,当此行被换出时才写回主存

- 减少访问主存的次数,存在不一致隐患

-

全写法

- cache与主存同时发生修改,较好维护了内容一致性

- 无需设置修改位,缺点是cache对cpu向主存的写操作无高速缓冲功能,降低了cache的功效

-

写一次法

基于写回法和全写法的写策略,处理方法与写回法基本相同,只是第一次写命中是要同时写入主存

-

ps

- 对存储器的要求是容量大速度快成本低,因此计算机采用多级存储体系结构

- 缓存速度与cpu速度相匹配,容量与缓存中数据的命中率有关

- 主存可由RAM和ROM组成

- 可编程的只读存储器不一定是可改写的

- 常用的虚拟存储器寻址系统由主存-辅存两级存储器组成

- 在程序的执行过程中,cache与主存的地址映射由硬件自动完成

- 芯片还需要1根片选线,1根读写线,一共是19根

- 采用虚拟存储器的主要目的是扩大主存储器的存储空间,并能进行自动管理和调度

网站声明:如果转载,请联系本站管理员。否则一切后果自行承担。

- 上周热门

- Kingbase用户权限管理 2020

- 信刻全自动光盘摆渡系统 1749

- 信刻国产化智能光盘柜管理系统 1419

- 银河麒麟添加网络打印机时,出现“client-error-not-possible”错误提示 1013

- 银河麒麟打印带有图像的文档时出错 923

- 银河麒麟添加打印机时,出现“server-error-internal-error” 714

- 麒麟系统也能完整体验微信啦! 657

- 统信桌面专业版【如何查询系统安装时间】 632

- 统信操作系统各版本介绍 623

- 统信桌面专业版【全盘安装UOS系统】介绍 597

- 本周热议

- 我的信创开放社区兼职赚钱历程 40

- 今天你签到了吗? 27

- 信创开放社区邀请他人注册的具体步骤如下 15

- 如何玩转信创开放社区—从小白进阶到专家 15

- 方德桌面操作系统 14

- 我有15积分有什么用? 13

- 用抖音玩法闯信创开放社区——用平台宣传企业产品服务 13

- 如何让你先人一步获得悬赏问题信息?(创作者必看) 12

- 2024中国信创产业发展大会暨中国信息科技创新与应用博览会 9

- 中央国家机关政府采购中心:应当将CPU、操作系统符合安全可靠测评要求纳入采购需求 8